# KHP 헬기탑재 임무컴퓨터 개발에 관한 연구

천 기진\* 염 문철\*\*

A Study on Development of Mission Computer for KHP

Chun, Ki Jin\* Yum, Chul Moon\*\*

내용목차

- 1. 서론

- 2. KHP 임무컴퓨터의 운용개념

- 3. 비행체 임무컴퓨터의 발전추세

- 4. KHP 임무컴퓨터의 개발방안

- 5. 결론

<sup>\*</sup> 넥스원퓨처(주)연구개발본부/항전연구소 소장

<sup>\*\*</sup> 넥스원퓨처(주)연구개발본부/항전연구소 수석연구원

# KHP 헬기탑재 임무컴퓨터 개발에 관한 연구

# A Study on Development of Mission Computer for KHP

### **Abstract**

Today's mission computer is needed to have open system architecture, hardware-independent software-development structure using open-oriented language, real-time large volume data processing, high-speed I/O processing and high reliability. Also to conform military environmental requirement. This paper describe development plane of KHP Mission Computer which meet these requirements.

<Key words> Mission Computer, Open Architecture, RTOS, VME64x

# 1. 서 론

현대 군용 항공전자장비들은 정보집중적이고 점차적으로 대규모 체계구조를 갖는 노드기능을 수행하는 추세이다. 이러한 기능들은 슈퍼컴퓨터 수준의 데이터처리능력과 대용량정보의 저장, 효과적인 인간-기계 인터페이스가 요구된다. 항공전자아키텍처는 전체적으로 실시간 성능, 신뢰성, 군용 항공기의 환경적인 요구사항 등이 반영된 시스템구조가 요구되어지며, 이러한 항공전자아키텍처를 구성하기 위해서는 항공전자아키텍처의 메인시스템인 임무컴퓨터의 성능 또한 데이터의 실시간 처리능력, 높은 신뢰성, 군용의 환경에 적합한 특성을 가져야만한다.[1] 본 논문에서는 이러한 요구사항을 만족시키도록 개발되고 있는 KHP 헬기탑재 임무컴퓨터의 개발방안을 기술하였다.

### 2. KHP 임무컴퓨터의 운용지침

먼저, KHP 임무컴퓨터는 KHP 항공전자체계(Mission Equipment Package, 이 하 MEP로 약칭)를 관리 및 운용하는 주제어컴퓨터로서, KHP의 임무수행에 필요한 각종 전술데이터의 처리와 MIL-STD-1553B 데이터버스를 통한 MEP 체계상의 항법, 통신, 식별의 CNI 계통 및 다기능 시현기(Multi-function Display, 이하 MFD), 통제시현장치(Control Display Unit, 이하 CDU), 헬맷장착 시현기(Helmet Mounted Display, 이하 HMD로 약칭) 등의 임무관리/시현계통의 통합및 통제를 수행한다.

임무컴퓨터에 탑재된 비행운용 소프트웨어(Operational Flight Program, 이하 OFP로 약칭)를 통하여 항법정보 및 헬기의 시스템상태 등과 관련된 각종 그래픽 심벌을 생성하고 디지털지도를 생성하여 MFD 상에 전시해 주는 역할을 수행한다. 즉, KHP 임무컴퓨터는 KHP헬기의 MEP체계의 두뇌와 같은 역할로서 MEP체계의 모든 하부시스템을 관장하는 역할을 수행한다.

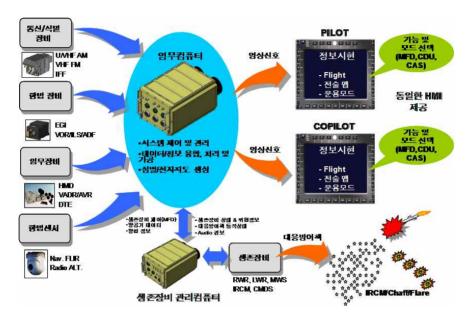

<그림 1> KHP 항전시스템의 동작 개념도

그리고, <그림 1>은 KHP 항전시스템의 운용개념을 나타내는데, KHP MEP 체계에서는 항전시스템의 신뢰도를 높이기 위하여 임무컴퓨터를 백업구조로 구 성하고 2대의 임무컴퓨터를 적용한다. 두 임무컴퓨터 사이에는 고속의 이더넷 (Ethernet) 인터페이스를 적용하여 실시간으로 데이터를 주고 받는다.

정·부조종사는 CDU 및 MFD, HMD를 통하여 항전시스템에 대한 통제 및 관리를 수행하는데, 임무컴퓨터가 4개의 MFD 상에 전시한 비행정보, 엔진, 유압 등 KHP 헬기시스템에 대한 정보, 전자지도 그리고 생존계통의 위협정보를 통하여 조종사가 원하는 임무를 수행한다.

<그림 2> KHP 임무컴퓨터 운용개념도

또한 <그림 2>는 KHP 임무컴퓨터의 운용개념을 나타내고 있다.

KHP 임무컴퓨터는 U/VHF AM 무전기, VHF FM 무전기 등의 통신계통, Embedded GPS/INS 등의 항법계통 및 임무장비, FLIR (Forward looking Infra Red) 센서 등의 각 KHP MEP 체계의 각 서브시스템으로부터 입력받은 정보 및 신호를 융합하고 연산/처리하여 시스템제어 및 관리를 하게 되며, 전자지도, 항법 및 엔진/유압 등 시스템관련 그래픽심벌을 생성하여 MFD 상에 정보시현을 하게된다. 또한 생존관리컴퓨터와 생존장비상태 그리고 위협정보, 대응방어책정보 등을 공유함으로써 조종사에게 생존계통에서 처리된 정보를 알려주는 역할을 수행한다[2].

### 3. 비행체 임무컴퓨터의 발전추세

현대 군용항공기의 항공전자시스템은 전자기술 및 컴퓨터기술의 급속한 발전에 힘입어 성능, 신뢰성, 프로그램작성의 용이성, 성장성 및 소형화를 추구하여 구세대 항공전자장비들의 체계통합화가 이루어지고 있으며, 또한 통신, 항법, 탐색 및 식별, 정찰, 공격, 전자전 등 다양한 임무요구에 따라 점차 다양화되고 세분화되고 있다. 이와 같은 통합화는 시스템구조를 간단하게 하고 전체 장비의 수를 대폭 줄여 소형, 경량화를 이룰 뿐 아니라, 항공전자기능에 따른 각 비행운용 소프트웨어(OFP)들을 하나로 통합할 수 있어, 프로그램의 작성 및 유지가 용이해진다.

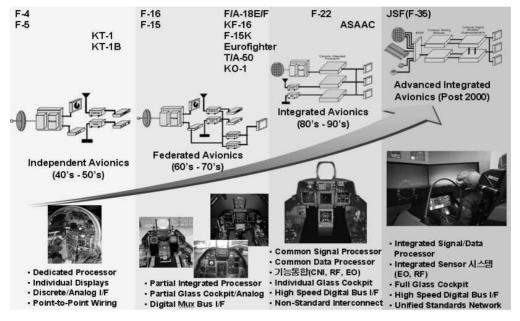

<그림 3> 항공전자 아키텍처 발전방향

1세대 독립형(아날로그) 항공전자시스템은 개별적인 기능을 구현하기 위한 전용의 센서, 프로세서, 시현장치들이 'point to point'로 연결되어 독립적으로 각각의 기능들이 수행되었었다. 연방형 아키텍처구조는 현재 운용되는 대부분의 군용항공기의 아키텍처로서, '시분할 다중화버스(MIL-STD-1553, STANAG 3910)'를

이용하여 일부 자원을 공유하며, 항법, 무장관리, 비행조종과 같은 다수의 표준데이터 프로세서를 사용하고 있다.

F-22, B777/787 민항기 및 F-35 프로그램들을 통해 이러한 이전 세대의 항공 전자아키텍처는 모듈식(modular), 통합형(integrated), 개방형의 구조와 Glass Cockpit 구조를 적용한 통합형 항공전자 시스템아키텍처로 발전하고 있다. <그림 3>은 이러한 항공전자 아키텍처의 발전방향을 도식화한 그림이다.

한편, 이전의 군용항공기의 임무컴퓨터는 전통적으로 폐쇄적이고 각각의 플랫폼에 의존적인 설계구조를 갖고 있었다. 그러나, 개발측면에서 비용/기간의 절감측면이 대두되고, 하위의 서브시스템들이 점차 플랫폼에 독립적인 구조를 가짐에따라 임무컴퓨터도 점차 폭넓은 상용기술을 채택하여, VME64 버스와 같은 대중적이고 공개적인 시스템버스를 채택하는 등 개방형구조의 임무컴퓨터가 개발되기 시작하였다. 또한, 현대전장에서는 조종사에게 보다 많은 정보를 바탕으로 한선택적 정보이용과 전술적 판단이 요구되기 때문에 임무컴퓨터는 보다 고속화되고 빠른 실시간 데이터처리를 요구받고 있다.

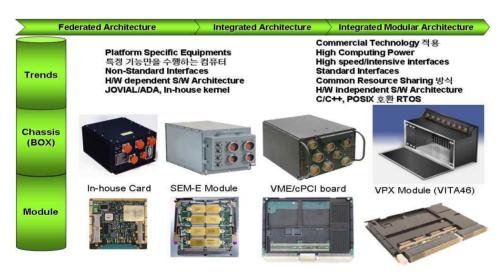

<그림 4> 임무컴퓨터의 하드웨어 발전추세

따라서, 최신의 임무컴퓨터는 다양한 항전계통으로부터 실시간으로 데이터를 수집, 처리 그리고 융합할 수 있도록, 고성능의 프로세서와 대용량 메모리, 고속 의 데이터버스, 실시간 운영체제를 채택하고 있다.

또한, 표준인터페이스와 Commercial Off-the-shelf (이하, COTS) 모듈의 적용 등 개방형구조가 채택됨에 따라, 임무컴퓨터에 적용되는 어플리케이션 소프트웨어 역시 널리 사용되고 있는 C/C++ 및 Portable Operating System Interface X (이하, POSIX로 약칭) 호환상용 Real-Time Operating System (이하, RTOS로 약칭), Application Programming Interface (이하, API로 약칭), 객체지향적 개발구조를 적용한 하드웨어에 독립적인 구조로 개발되고 있다. <그림 4>는 이러한 임무컴퓨터의 하드웨어의 발전추세를 나타낸 그림으로, 초창기의 In-house Card 형식의 폐쇄적인 개발구조에서 VME 및 VPX 구조의 개방형 구조로 진보하는 모습을 나타내고 있다.

| Fe        | ederated Architecture        | Integrated Architecture                                         | Integrated Modular Architecture                          |  |

|-----------|------------------------------|-----------------------------------------------------------------|----------------------------------------------------------|--|

| nterfaces | Item                         | Past I/F                                                        | Current/Future I/F                                       |  |

|           | System Bus                   | VME, PCI                                                        | VPX, Serial Switched Fabric, PCIe                        |  |

|           | Aircraft I/O,<br>Cockpit I/O | RS-232/422/485,<br>Analog/Discrete,<br>MIL-STD-1553A, ARINC-429 | RS-232/422, Analog/Discrete,<br>MIL-STD-1553B, ARINC-653 |  |

|           | Sensor I/F                   | RS-232/422/485                                                  | Serial RapidIO, Infiniband, RoketIC                      |  |

|           | Storage I/F                  | SCSI, IDE                                                       | Fibre Channel, SATA, SCI                                 |  |

|           | Video I/F                    | Analog (RS-170A)                                                | Digital Video (LVDS, DVI)                                |  |

|           | Flight Control I/F           | MIL-STD-1553A/B                                                 | IEEE1394(Firewire)                                       |  |

| oftware   | ltem                         | Past I/F                                                        | Current/Future I/F                                       |  |

|           | Operating System             | In-house Kernel                                                 | POSIX Compliant RTOS                                     |  |

|           | Language                     | JOVIAL, Ada                                                     | C/C++, UML                                               |  |

|           | Graphics Language            | Custom Graphics Driver                                          | OpenGL                                                   |  |

|           | Language                     | ASM, JOVIAL, Ada                                                | C/C++, UML                                               |  |

<그림 5> 임무컴퓨터 인터페이스/소프트웨어 발전 추세

또한, <그림 5>는 임무컴퓨터의 인터페이스 및 소프트웨어의 발전추세를 나타 낸 그림으로서, 인터페이스도 점차 아날로그 및 시리얼 인터페이스에서 고속의 Serial Rapid IO 나 Ethernet 과 같이 고속데이터를 처리할 수 있는 인터페이스 구조로 변경되고 있으며, 소프트웨어도 In-House Kernel 및 Custom Graphics Driver 등 폐쇄적 구조에서 RTOS 및 OpenGL과 같은 개방형 및 상업용 소프트 웨어를 적용하여 하드웨어에 독립적인 소프트웨어구조로 발전하고 있다[3].

### 4. KHP 임무컴퓨터의 개발방안

## 4.1 개발목표의 사양

KHP 임무컴퓨터는 다음 그림 MEP 체계의 여러 임무탑재장비에 대한 시스템의 통제 및 관리 기능, 항법정보계산과 비행데이터의 처리 및 융합기능, 전자지도의 프로세싱기능과 MFD, CDU용 라스터 그래픽 심벌생성기능, 시스템 비디오의 영상처리 및 혼합, 관리기능 등을 제공해야 한다.

이에 따른 KHP 임무컴퓨터의 개발목표성능은 다음 <표 1>과 같다.

<표 1> KHP 임무컴퓨터의 개발목표성능

| 항목           | 목표성능                                                                                                                                               | 비고                      |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 프로세서         | PPC-7447 (1.0础) 혹은 동등이상                                                                                                                            | SPM, GPM, DMM<br>모듈에 내장 |

| 메모리          | <ul> <li>데이터메모리(SDRAM): 1GB</li> <li>프로그램메모리: 512MB</li> <li>비 휘발성메모리: 128KB</li> <li>LEVEL 2 Cache: 2MB</li> </ul>                                |                         |

| 시스템 버스       | VME 64 표준버스                                                                                                                                        |                         |

| 1553B 데이터 버스 | 2 채널 이상                                                                                                                                            |                         |

| 비디오 입/출력     | 송신 :DVI 8채널, 수신 NTSC, RGB 각<br>1채널 이상                                                                                                              |                         |

| ARINC 429    | 송신 4채널, 수신 8채널 이상                                                                                                                                  |                         |

| 자체점검기능       | PBIT, CBIT, IBIT                                                                                                                                   |                         |

| MTBF         | MIL-HDBK-217F 신뢰분석기법 적용                                                                                                                            |                         |

| 운영체제         | RTOS, VxWorks 6.x 이상                                                                                                                               |                         |

| 그래픽 라이브러리    | OpenGL                                                                                                                                             |                         |

| 전원입력         | ■ 동작전원 18~32Vdc<br>■ Hold-Up Time: 50ms                                                                                                            | MIL-STD-704F            |

| 전자기적합성       | <ul> <li>전도방사: CE-101, CE-102</li> <li>전도내성: CS-101, CS-114, CS-115, CS-116</li> <li>복사방사: RE-101, RE-102</li> <li>복사내성: RS-101, RS-103</li> </ul> | MIL-STD-461E            |

| 환경           | ■ 온/고습도, 진동, 충격                                                                                                                                    | MIL-STD-810F            |

### 4.2 하드웨어의 구조

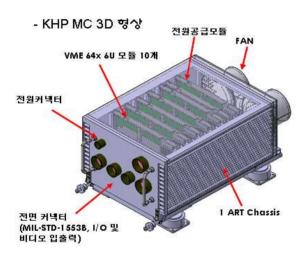

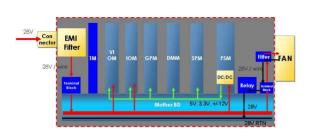

KHP 임무컴퓨터의 하드웨어구조는 다음 <그림 6>과 같이 개방형 구조를 채택하여 산업표준 버스구조인 VME 64x 구조를 기본 백플레인(Backplane) 구조로 채택하였다. 하드웨어구조의 주요 특징은 다음과 같다.

<그림 6> KHP 임무컴퓨터 하드웨어 구조형상

- Open/Modular System Architecture 구조

- 산업표준 인터페이스 사용:

VME64X, PCI, Ethernet 등

- Hardware Independent Open Architeture 구조.

- VME 6U 표준크기 및 VME 64

Backplane bus 적용

- Centalized Processing

- COTS SBC, IEEE 1003.1 POSIX 호환 RTOS

- Open Graphic Language (OpenGL)

- Hot-BackUp Redunancy 구조

### 4.3 모듈구성의 개관

KHP 임무컴퓨터의 구성모듈은 개방형 구조의 특성에 맞게 기존 COTS제품 싱글보드 컴퓨터(7447 보드)와 1553 카드, 그래픽 PCI Mezzanine Card (이하, PMC), 대용량메모리 PMC를 적용한 System Processor Module (이하, SPM로 약칭), Graphic Processor Module (이하, GPM로 약칭), Digtal Map Module (이하, DMM로 약칭)과 KHP MEP 체계에 맞도록 설계된 In-house 구조의 Video In Out Module (이하, VIOM로 약칭) 및 In-Out Module (이하, IOM로 약칭) 그리고 KHP 전원요구 특성에 맞도록 재수정 개발된 COTS 전원공급기로 구성되어 있다. <그림 7>은 임무컴퓨터의 모듈구성을 나타내고 있다.

# System Processor Module (SPM) Video Input/Output Processor Module (VIOPM) Input/Output Module (IOM) Power Supply Module (PSM)

■ Graphics Processor Module (GPM)

<그림 7> KHP 임무컴퓨터 모듈 구성

### 4.4 개발목표의 성능

### 1) 시스템구성

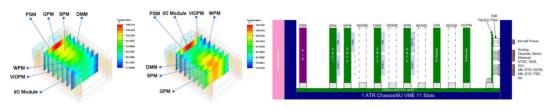

KHP 임무컴퓨터의 시스템구성은 백 플레인(Backplane)인 VME64X 구조의 마더보드를 기반으로 각각의 모듈에 대한 열 해석을 수행하였으며, VME 규격 및 고속신호 등 주요 인터페이스 신호에 관한 전기적 신호특성 등을 고려하여 전체적인 임무컴퓨터 배치구조를 구성하였다. <그림 8>은 각 모듈의 열 해석 수행결과를 나타내며, <그림 9>는 임무컴퓨터 각 모듈의 배치 구조를 나타낸다. 발열량이 가장 많은 전원공급기가 팬과 가장 가깝게 배치되며, 인터페이스 관련된 IOM 모듈과 고속 비디오신호의 입/출력을 담당하는 VIOM 모듈이 전면판 쪽에 배치된다.

<그림 8> 임무컴퓨터 열 해석 결과

<그림 9> 임무컴퓨터 모듈배치 구조

### 2) I/O 인터페이스

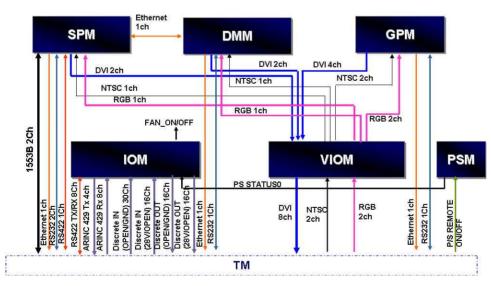

KHP 임무컴퓨터는 KHP MEP 체계와 연동하기 위하여 다양한 I/O 인터페이스를 요구받고 있으며, 산업표준의 인터페이스를 적용이 요구된다. 따라서 임무컴퓨터는 KHP MEP 체계상의 모든 하위시스템을 통제하기 위하여 기본적으로 2개의 MIL-STD-1553B를 사용하며 PCI, Ethernet, ARINC 429, RS422 및 디스크리트 I/O 등과 같은 산업표준의 인터페이스를 적용하며, 이외에 외부장비와의다양한 인터페이스기능을 제공한다. 다음 <그림 10>은 KHP 임무컴퓨터의 다양한 인터페이스를 나타내고 있다. TM 모듈은 마더보드와 전면판 외부연결용 커넥터 사이의 인터페이스 모듈이다.

<그림 10> KHP 임무컴퓨터 인터페이스 구성도

### 3) 고성능 프로세싱능력

KHP 임무컴퓨터는 실시간으로 대용량의 데이터를 수집, 처리 및 융합할 수 있도록 고성능 프로세스가 탑재된 PPC7447A 싱글보드 컴퓨터를 메인 CPU 모듈로 사용하며, 전자지도와 같은 3-D 그래픽을 시현하기 위하여 그래픽전용모듈로 사용한다. <그림 11>은 PPC7447A SBC 의 형상이다.

<그림 11> PPC7447A SBC

- 프로세서: PPC7447A, 1.0GHz

- 메모리: 1 GB DDR SDRAM

- flash 512MB

- PCI Controller: Discovery III(64460)

- PCM 구성

- PMC1 (32,64Bit/33,66,133MHz)

- PMC2 (32,64Bit/33,66,100 MHz)

- Ethernet : 3 채널

### 4) 고속 비디오신호 인터페이스

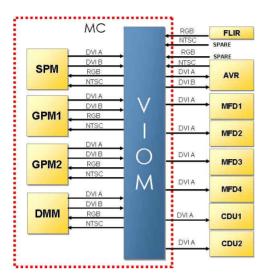

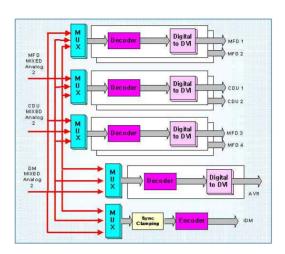

KHP 임무컴퓨터는 정·부 조종사에게 인간-기계(man-machine) 인터페이스를 제공하기 위하여 4개의 MFD와 2개의 CDU에 항법정보, 전자전정보, 헬기 시스템정보 등 다양한 정보를 시현하여야 한다. 따라서, 고속의 비디오신호를 인터페이스해야 하는 성능이 요구된다.

<그림 12>와 같이 MFD, CDU로의 비디오 출력신호는 디지털 비디오신호 (Digital Visual Interface 이하 DVI) 형식의 신호를 사용하며 FLIR 등으로 부터의 비디오 입력신호는 National Television System Committee (이하 NTSC) 및 RGB 형식의 신호를 사용한다. <그림 13>은 이러한 비디오 입/출력 신호간의 스위칭 역할을 수행하는 VIOM 모듈을 나타내고 있다.

<그림 12> 임무컴퓨터 비디오 입/출력

<그림 13> VIOM 모듈 구성안

- In- House 개발

- 4개 MFD 및 2개 CDU로 영상 출력

- DVI 비디오출력 : 7 채널

- 아날로그 비디오출력: 1 채널

- 6:1 MUX 5채널

- 7개의 DVI 변환회로

- 디코더 기능

- VME 인터페이스

### 5) 전자기 및 환경조건

KHP 임무컴퓨터에 적용되는 전자기의 적합성(EMI) 조건 및 환경조건은 다음과 같다. 전자기의 적합성 조건은 MIL-STD-461E를 적용하며, 온/고습도 및 진동, 충격에 관한 환경조건은 MIL-STD-810F를 적용한다. 세부 적용항목은 <표2>와 같다.

### 6) 전원특성

KHP 임무컴퓨터의 전원은 KHP헬기의 뱃터리버스로부터 28VDC의 직류 입력전원을 공급받으며, MIL-STD-704F의 규격을 적용받는다. 또한 MIL-STD-

704F의 엔진 시동조건에서도 동작하여야 한다. 따라서 이러한 전원특성을 만족 시킬 수 있도록 해외 COTS 전원공급기를 개조하고 및 설계 변경하여 적용한다.

<표 2> 임무컴퓨터 전자기 적합성(EMI) 및 환경적용 규격

| 구분         | 세부 적용항목 | 적용 규격                                        |                                                                      |

|------------|---------|----------------------------------------------|----------------------------------------------------------------------|

|            | СЕ      | CE101                                        | Power Leads, 30Hz to 10kHz                                           |

|            |         | CE102                                        | Power Leads, 10kHz to 10MHz                                          |

|            | CS      | CS101                                        | Power Leads, 30Hz to 150kHz                                          |

|            |         | CS114                                        | Bulk Cable Injection, 10kHz to 200MHz                                |

|            |         | CS115                                        | Bulk Cable Injection, Impulse Excitation                             |

| 전자기<br>적합성 |         | CS116                                        | Damped Sinusoidal Transients, Cable and Power Leads, 10kHz to 100MHz |

| 조건         | RE      | RE101                                        | Magnetic Field, 30Hz to 100kHz                                       |

|            |         | RE102                                        | Electric Field, 10kHz to 18GHz                                       |

|            | RS      | RS101                                        | Radiated Susceptibility, Magnetic Field, 30Hz to 100kHz              |

|            |         | RS103                                        | Radiated Susceptibility, Electric Field, 2Mb to 400b                 |

|            | 온/고/습도  | MIL-STD-810F Method 520.2 Procedure III      |                                                                      |

|            |         | 온도 -35℃~+55℃(동작), -50℃~+85℃(저장)              |                                                                      |

| 환경조건       |         | 고도 15,000Ft                                  |                                                                      |

| せつエゼ<br>   |         | 습도 32℃~60℃, RH 85~95%                        |                                                                      |

|            | 진동      | MIL-STD-810F, Method 514.5 Procedure I       |                                                                      |

|            | 충격      | MIL-STD-810F, Method 516.5 Procedure I & III |                                                                      |

<그림 14> 는 임무컴퓨터의 내부전원 공급구조를 나타내며, <그림 15>는 개조변경에 적용되는 COTS 전원공급기의 형상을 나타내고 있다. <그림 14>에서 28V DC 직류전원은 마더보드를 통하여 전원공급기 및 팬(FAN)으로 공급되고 있으며, 마더보드는 팬 구동회로를 내장하고 있다.

<그림 14> 임무컴퓨터 내부 전원공급 구조

<그림 15> Modified COTS 전원공급기

### 7) 소프트웨어

임무컴퓨터의 소프트웨어는 다음 <그림 16>과 같은 하드웨어에 독립적인 구조를 가지고 있다. Target H/W PowerPC 7447A에 Device Driver, BSP 및 RTOS Kernel 로는 VxWorks 6.x 버전이 탑재되어 있으며, 3D 그래픽 구현을 위한 OpenGL Driver를 적용하고 있다. 이와 같은 OFP 실행환경 소프트웨어의 상위에는 OFP가 탑재되어진다.

<그림 16> 임무컴퓨터 OFP 실행환경 소프트웨어

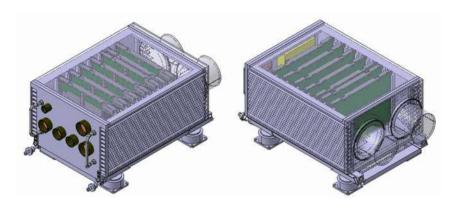

### 8) 기구물

KHP 임무컴퓨터의 기구물은 1 ATR Long Chassis 사이즈로 다음 <그림 17>과 같은 형상을 가지며 285(W)×514.7(D)×240.2(H)의 사이즈와 21.56kg의 목 표중량으로 설계한다. 열 해석을 바탕으로 임무컴퓨터 Cooling에 가장 효율이 좋은 FAN을 선정하였으며, 유동관로도 설계한다.

Ⅱ 크게(Tray포함): 285.0(M)x514.7x(D)x240.2(H)

| 무개: 21.56Kg

<그림 17> KHP 임무컴퓨터의 기구물 외부 형상

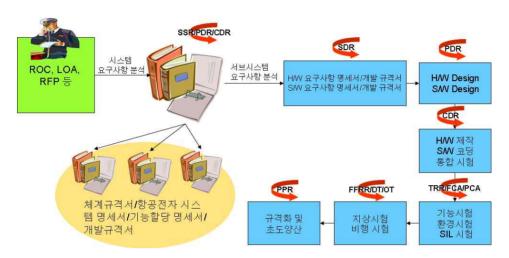

### 4.5 개발설계의 절차

임무컴퓨터의 설계절차는 <그림 18>과 같다. 수요군의 Required Operational Capability (ROC), Letter Of Agreement (LOA) 및 Request For Proposal (RFP) 가 제공되면 시스템 요구사항 분석을 통하여 H/W 및 S/W 요구사항 명세서와 개발 규격서를 작성하며, 기본설계검토(PDR) 및 상세설계검토(CDR)을 거쳐 실제 임무컴퓨터를 설계하고 제작한다.

임무컴퓨터가 제작되면 기능시험과 환경시험 등을 통하여 임무컴퓨터의 기능 및 성능을 검증하게 되고, KHP 헬기탑재 전 System Integration Laboratory (이 하, SIL로 약칭)의 실험실 환경에 장착하여 인터페이스 및 성능을 다시 검증하게 되며 SIL 시험완료 후, 헬기의 지상시험 및 비행시험을 수행한다.

이렇게 여러 단계의 과정을 거쳐 수요군의 최종 'Development Test (DT)'와 'Operation Test (OT)'까지 완료한 이후에는 규격화과정과 양산단계로 넘어가 수요 군에 납품되는 양산제품을 생산하는 것이다.

<그림 18> KHP 임무컴퓨터 개발단계

### 5. 결 론

본 논문에서는 KHP 임무컴퓨터의 운용개념을 살펴보았고, 항공전자 시스템 아키텍처와 임무컴퓨터의 발전추세를 바탕으로 KHP 임무컴퓨터의 개발방안에 대하여 기술하였다.

현대의 임무컴퓨터는 하드웨어의 개방형 아키텍처 구조와 소프트웨어의 하드웨어에 독립적인 객체지향적 개발구조가 요구되며, 대용량 데이터의 실시간 처리능력, 고속 신호 I/O 처리능력, 높은 신뢰성, 군용의 환경에 적합한 특성 등이 요구되어진다.

KHP 임무컴퓨터는 이러한 요구조건에 부합하도록 VME64X 버스의 개방형 구조를 채택하였으며, 상용 COTS 제품 및 고속 비디오신호, IO 신호를 처리할 수 있도록 설계하고 있다. 또한 확장성이 고려된 설계를 통하여 후속 개발사업인 공격형헬기, 한국형전투기사업(KFX), 성능개량사업 등에도 적용가능하다. 향후 개발절차에 따라 기능, 성능시험, 환경시험과 SIL시험, 지상시험과 비행시험을 통하여 개발된 KHP 임무컴퓨터의 성능을 검증할 예정이다.

### 참고문헌

- [1] 이재동, 염철문, 이재억, 박재성, "전투기의 항공전자 아키텍처에 관한 연구", 『항공우주 무기체계 발전 세미나 발표논문집』, 2006. 10.

- [2] 천기진, "KHP 헬기탑재 임무컴퓨터 개발", 『KHP 기술발전 세미나』, 2006. 4.

- [3] 천기진, "항공탑재 전자장비 기술개발", 『항공전자연구 심포지엄』, 2006. 11.